很多世界顶尖的“建筑师”可能是你从未听说过的人,他们设计并创造出了很多你可能从未见过的神奇结构,比如在芯片内部源于沙子的复杂体系。如果你使用手机、电脑,或者通过互联网收发信息,那么你就无时无刻不在受益于这些建筑师们的伟大工作。

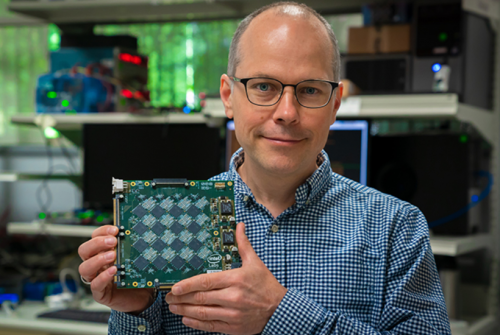

Doug Burger博士就是这群“建筑师”里的一员。他现任微软技术院士(Technical Fellow),曾任微软研究院杰出工程师、德克萨斯大学奥斯丁分校计算机科学教授。他也是微软FPGA项目Catapult和Brainwave的首席架构师和主要负责人。2018年,Doug Burger在微软研究院的播客里分享了他对后摩尔定律时代芯片产业发展的观点与愿景,并展望了人工智能时代芯片技术的前进方向。

(Doug Burger博士,图片来自微软)

老石对他的观点进行了整理和采编。第一篇在这里。本文是第二篇,主要是Doug Burger博士对FPGA在人工智能时代的独特优势的全面分析,以及他对于人工智能技术发展的深刻思考。文章很长,但全部是他几十年从业经验的深入浅出的阐述,尽显大师之风,值得一读。

注,下文中的“我”,指的都是Doug Burger博士。

目 录

1. 什么是暗硅效应

2. FPGA:解决暗硅效应的有效途径

3. 使用FPGA的独特优势是什么

4. 什么是Catapult项目

5. 脑波项目与实时AI

6. 评价实时AI系统的主要标准

7. AI未来的发展路在何方?

1. 什么是暗硅效应

在我加入微软之前,我和我的博士生Hadi Esmaeilzadeh正在开展一系列研究工作。他现在已经是加州大学圣地亚哥分校的副教授。在当时,学术界和业界的主要发展趋势就是多核心架构。虽然尚未完全成为一个正式的全球性共识,但多核架构是当时非常热门的研究方向。人们认为,如果可以找到编写和运行并行软件的方法,我们就能直接将处理器架构扩展到数千个核心。然而,Hadi和我却对此不以为然。

于是,我们在2011年发表了一篇论文,并因此获得了很高的知名度。虽然在那篇论文里没有明确的定义“暗硅(dark silicon)”这个词,但是它的意义却得到了广泛认可。

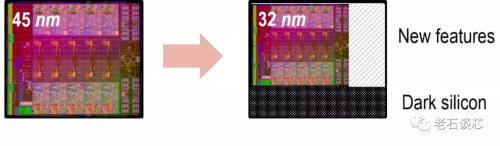

暗硅效应指的是,虽然我们可以不断增加处理器核心的数量,但是由于能耗限制,无法让它们同时工作。就好像一幢大楼里有很多房间,但由于功耗太大,你无法点亮每个房间的灯光,使得这幢大楼在夜里看起来有很多黑暗的部分。这其中的本质原因是在后摩尔定律时代,晶体管的能效发展已经趋于停滞。

(暗硅示意图,图片来自NYU)

这样,即使人们开发出了并行软件,并且不断增加了核心数量,所带来的性能提升也会比以往要小得多。所以,除此之外,业界还需要在其他方面带来更多进展,以克服“暗硅”的问题。

2. FPGA:解决暗硅效应的有效途径

在我看来,一个可行的解决方法就是采用“定制计算”,也就是为特定的工作场景和负载优化硬件设计。然而,定制计算或定制芯片的主要问题就是高昂的成本。例如对于一个复杂的云计算场景,不论是设计者还是使用者都不会采用一个由47000种不同的芯片所组成的系统。

因此,我们将赌注押在了这个名叫FPGA的芯片上。FPGA全名叫“现场可编程逻辑阵列”,它本质是一种可编程的芯片。人们可以把硬件设计重复烧写在它的可编程存储器里,从而使FPGA芯片可以执行不同的硬件设计和功能。另外,你也可以在使用现场动态的改变它上面运行的功能,这就是为什么它们被称作“现场可编程”的原因。事实上,你可以每隔几秒就改变一次FPGA芯片上运行的硬件设计,因此这种芯片非常灵活。

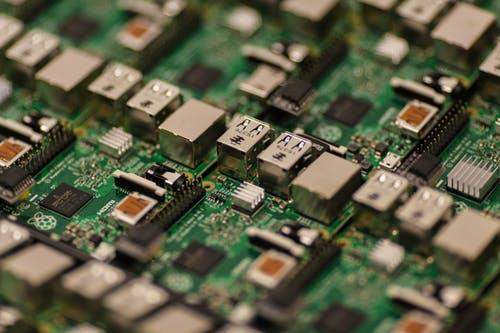

(英特尔Stratix 10 FPGA芯片,图片来自英特尔)

基于这些特点,我们在FPGA这项技术上押下重注,并且将其广泛的部署到了微软的云数据中心里。与此同时,我们也开始将很多重要的应用和功能,从基于软件的实现方式,慢慢转移到基于FPGA的硬件实现方式上。可以说,这是一个非常有趣的计算架构,它也将是我们的基于定制化硬件的通用计算平台。

通过使用FPGA,我们一方面可以尽早开展定制化计算与定制芯片的研究与设计,另一方面,我们可以保持与现有架构相互兼容的同构性。

如果具体的应用场景或算法发展的太快,或者硬件规模太小的时候,我们可以继续使用FPGA实现这些硬件功能。当应用规模逐渐扩大时,我们可以在合适的时机,选择将这些已经成熟的定制化硬件设计直接转化成定制化芯片,以提高它们的稳定性,降低功耗和成本。

灵活性是FPGA最重要的特点。要知道,FPGA芯片已经在电信领域中得到了非常广泛的使用。这种芯片非常擅长对数据流进行快速处理,同时也被用于流片前的功能测试等。但是在云计算中,之前并没有人能够真正成功的大规模部署FPGA。我指的“部署”,并不是指那些用来作为原型设计或概念验证的工作,而是指真正的用于工业级使用的部署。

3. 使用FPGA的独特优势是什么

首先我想说的是,CPU和GPU都是令人惊叹的计算机架构,它们是为了不同的工作负载与应用场景而设计的。

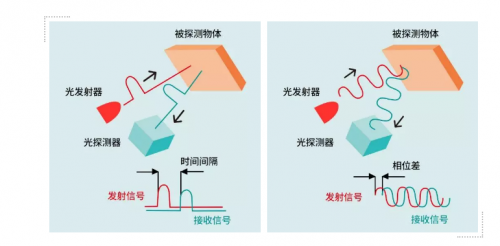

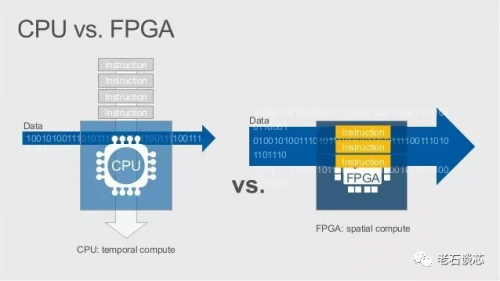

CPU是一种非常通用的架构,它的工作方式基于一系列的计算机指令,也称为“指令集”。简单来说,CPU从内存中提取一小部分数据,放在寄存器或者缓存中,然后使用一系列指令对这些数据进行操作。操作完毕后,将数据写回内存,提取另一小部分数据,再用指令进行操作,并周而复始。我把这种计算方式称为“时域计算”。

不过,如果这些需要用指令进行处理的数据集太大,或者这些数据值太大,那么CPU就不能很高效的应对这种情况。这就是为什么在处理高速网络流量的时候,我们往往需要使用定制芯片,比如网卡芯片等,而不是CPU。这是因为在CPU中,即使处理一个字节的数据也必须使用一堆指令才能完成,而当数据流以每秒125亿字节进入系统时,这种处理方式哪怕使用再多的线程也忙不过来。

对于GPU来说,它所擅长的是被称作“单指令多数据流(SIMD)”的并行处理。这种处理方式的本质是,在GPU中有着一堆相同的计算核心,可以处理类似但并不是完全相同的数据集。因此,可以使用一条指令,就让这些计算核心执行相同的操作,并且平行的处理所有数据。

然后对于FPGA而言,它实际上是CPU计算模型的转置。与其将数据锁定在架构上,然后使用指令流对其处理,FPGA将“指令”锁定在架构上,然后在上面运行数据流。

(CPU与FPGA计算模型的对比,图片来自微软)

我把这种计算方式称为“结构计算”,也有人称之为“空间计算”,与CPU的“时域计算”模型相对应。其实叫什么名称都无所谓,但它的核心思想是,将某种计算架构用硬件电路实现出来,然后持续的将数据流输入系统,并完成计算。在云计算中,这种架构对于高速传输的网络数据非常有效,并且对于CPU来说也是一个很好的补充。

4. 什么是Catapult项目

Catapult项目的主要目的是在微软的云数据中心大规模部署FPGA。虽然这个项目涵盖了电路和系统架构设计等工程实践,但它的本质还是一个研究项目。

在2015年末,我们开始在微软购买的几乎每台新服务器上部署Catapult FPGA板卡。这些服务器被用于微软的必应搜索、Azure云服务以及其他应用。到目前为止,我们已经发展到了非常大的规模,FPGA已经在世界范围内被大规模部署。这也使得微软成为了世界上最大的FPGA客户之一。

(Catapult FPGA板卡,图片来自微软)

在微软内部,很多团队都在使用Catapult FPGA来增强自己的服务。同时,我们使用FPGA对云计算的诸多网络功能进行加速,这样我们的客户会得到比以往更加快速、稳定、安全的云计算和网络服务。比如,当网络数据包以每秒500亿比特的速度进行传输时,我们可以使用FPGA对这些数据包进行控制、分类和改写。相反的,如果我们使用CPU来做这些事情的话,将需要海量的CPU内核资源。因此,对于我们这样的应用场景,FPGA是一个更好的选择。

(微软的FPGA板卡,图片来自微软)

5. 脑波项目与实时AI

当前,人工智能有了很大的发展,而这很大程度上归功于深度学习技术的发展。人们逐渐认识到,当你有了深度学习算法、模型,并构建了深度神经网络时,需要足够多的数据去训练这个网络。只有加入更多的数据,才会让深度神经网络变的更大、更好。通过使用深度学习,我们在很多传统的AI领域取得了长足的进展,比如机器翻译、语音识别、计算机视觉等等。同时,深度学习也可以逐步替换这些领域发展多年的专用算法。

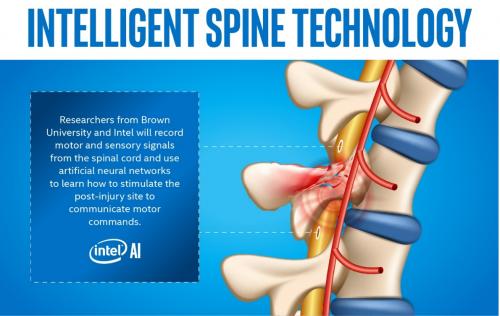

这些巨大的发展和变革,促使我思考它们对半导体和芯片架构的影响。于是,我们开始重点布局针对AI、机器学习、特别是深度学习的定制化硬件架构,这也就是脑波项目(Project Brainwave)产生的主要背景。

在脑波项目里,我们提出了一种深度神经网络处理器,也有人称之为神经处理单元,或者NPU(Neural Processing Unit)。对于像必应搜索这样的应用来说,他们需要很强的计算能力,因为只有不断学习和训练,才能向用户提供更优的搜索结果。

因此,我们将大的深度神经网络利用FPGA进行加速,并在很短的时间内返回结果。目前,这种计算架构已经在全球范围内运行了一段时间。在2018年的微软开发者大会上,我们正式发布了脑波项目在Azure云服务上的预览版。我们也为一些用户提供带有FPGA的板卡,使他们可以使用自己公司的服务器,从Azure上获取AI模型并运行。

(Brainwave FPGA板卡,图片来自微软)

对于脑波项目来说,另外一个非常重要的问题在于神经网络的推断。目前的很多技术使用的是一种叫做批处理的方法。比如说,你需要将很多个不同的请求收集到一起,然后打包发送到NPU进行处理,然后一次性得到所有的答案。

对于这种情形,我经常把它比喻成你在银行里排队,你排在第二个,但总共有100个人排队。出纳员将所有人的信息收集起来,并询问每个人想要办什么业务,然后取钱存钱,再把钱和收据发给每个人。这样每个人的业务都在同一时刻完成,而这就是所谓的批处理。

对于批处理应用来说,可以达到很好的吞吐量,但是往往会有很高的延时。这就是我们为什么在尝试推动实时AI的发展。

6. 评价实时AI系统的主要标准

评价实时AI的主要性能指标之一,就是延时的大小。然而,延时到底多小才算“够小”,这更像是一个哲学问题。事实上,这取决于具体的应用场景。比如,如果在网络上监控并接收多个信号,并从中分析哪个地方发生了紧急情况,那么几分钟的时间就算够快了。然而,如果你正在和某人通过网络进行交谈,哪怕是非常小的延时和卡顿也会影响通话质量,就像很多电视直播采访里经常出现的两个人在同时讲话那样。

另外一个例子是,微软的另一项人工智能技术是所谓的HPU,它被用于HoloLens设备中。HoloLens是一款智能眼镜,它能提供混合现实和增强现实等功能,它里面的HPU也具备神经网络的处理功能。

(宇航员Scott Kelly在国际空间站上使用HoloLens,图片来自NASA)

对于HPU,它需要实时分析使用者周围的环境,这样才能在你环顾四周时,无缝的展示虚拟现实的内容。因此在这种情况下,即使延时只有几个毫秒,也会对使用者的体验造成影响。

除了速度之外,另一个需要考虑的重要因素就是成本。举例来说,如果你希望通过处理数十亿张图像或数百万行文本,进而分析和总结出人们常问的问题或者可能在寻找的答案,就像很多搜索引擎做的那样;抑或是医生想要从很多放射扫描影像中寻找潜在的癌症指征。

那么对于这些类型的应用来说,服务成本就非常重要。在很多情况下,我们需要权衡以下两点,一个是系统的处理速度有多快,或者通过何种方式能提升处理速度;另一个就是对于每个服务请求或处理,它的成本有多少。

很多情况下,增加系统的处理速度势必代表着更多的投入和成本的攀升,两者很难同时满足。但这就是脑波项目的主要优势所在,通过使用FPGA,我认为我们在这两个方面都处于非常有利的位置。在性能方面我们是最快的,在成本上我们大概率也是最便宜的。

7. AI未来的发展路在何方?

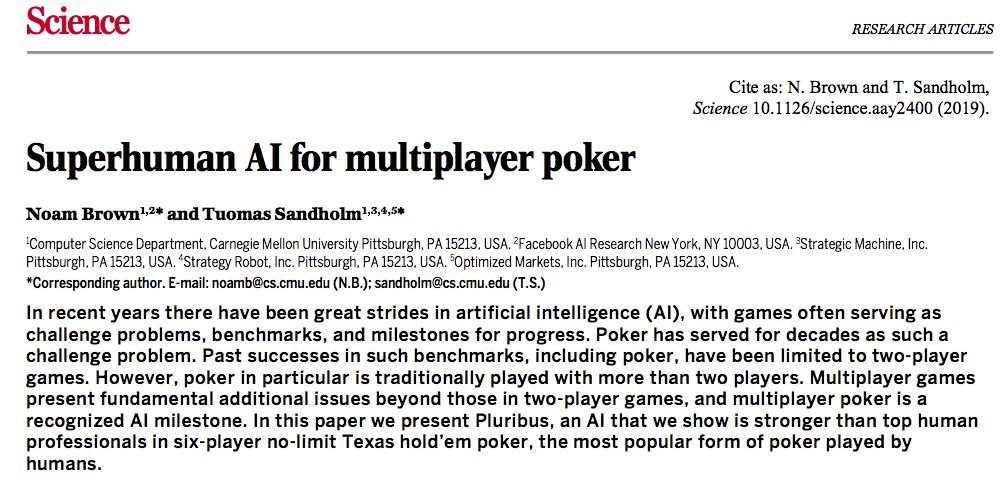

说实话,我一点也不担心人工智能的末日。相比任意一种现有的生物系统的智能,人工智能的效率还差着成千上万倍的距离。可以说,我们现在的AI其实并不算怎么“智能”。另外,我们也需要在道德层面关注和掌控AI的发展。

不管怎样,我们的工作从某种程度上提高了计算的效率,这使得它可以用来帮助解决重大的科学问题,我对此有很强的成就感。

对于那些正在考虑从事硬件系统和计算机架构研究的人来说,最重要的就是找到那颗能让你充满激情并为之不懈奋斗的“北极星”,然后不顾一切的为之努力。一定要找到那种打了鸡血的感觉,不用担心太多诸如职业规划、工作选择等问题,要相信车到山前必有路。你在做的工作,应该能让你感受到它真正能带来变革,并帮助你在变革的道路上不断前行。

当前,人们已经开始意识到,在我说的这些“后·冯诺依曼时代”的异构加速器之外,还有远比这些更加深刻的东西等待我们探寻。我们已经接近了摩尔定律的终点,而基于冯诺依曼体系的计算架构也已经存在了相当长的时间。自从冯诺依曼在上世纪四十年代发明了这种计算架构以来,它已经取得了惊人的成功。

但是现在,除了这种计算结构外,又产生了各种硬件加速器,以及许多人们正在开发的新型架构,但是从整体上来看,这些新结构都处在一个比较混乱的状态。

我认为,在这个混乱的表象之下,还隐藏着更加深刻的真理,而这将会是人们在下个阶段的最重要发现,这也是我目前经常在思考的问题。

我慢慢发现,那些可能已经普遍存在的东西会是计算架构的下一个巨大飞跃。当然,我也可能完全错了,但这就是科学研究的乐趣所在。